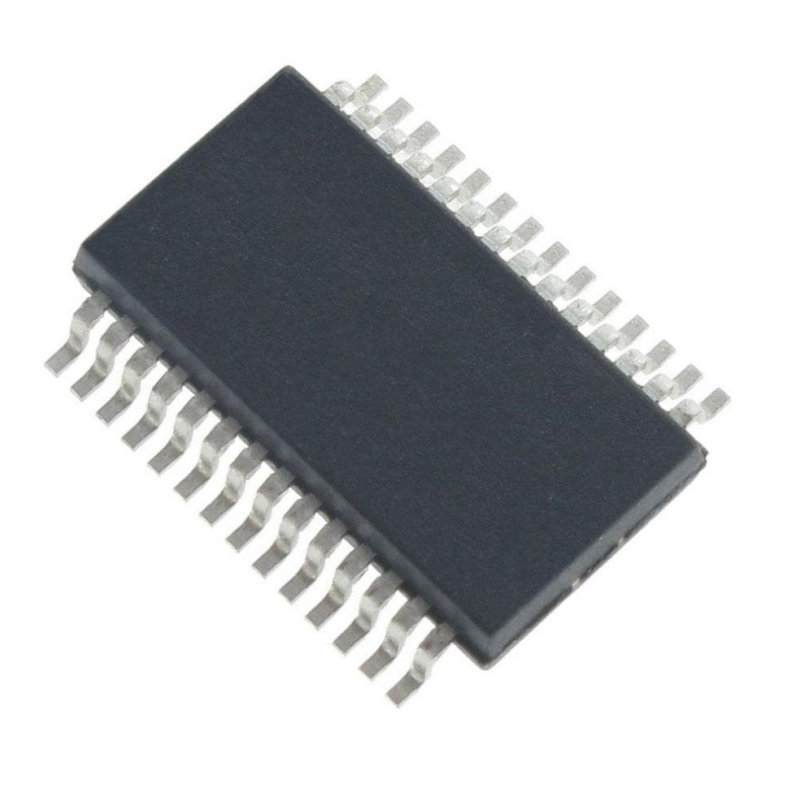

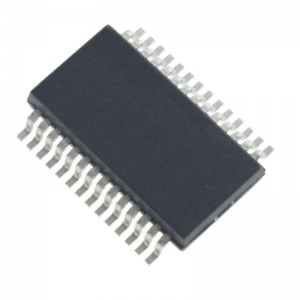

Microcontroladors PIC18F27Q84-I/SS de 8 bits, MCU CAN-FD, memòria flaix de 128 KB, RAM de 13 KB

♠ Descripció del producte

| Atribut del producte | Valor de l'atribut |

| Fabricant: | Microxip |

| Categoria de producte: | Microcontroladors de 8 bits - MCU |

| RoHS: | Detalls |

| Sèrie: | PIC18F27Q84 |

| Estil de muntatge: | SMD/SMT |

| Paquet / Caixa: | SSOP-28 |

| Nucli: | PIC18 |

| Mida de memòria del programa: | 128 kB |

| Amplada del bus de dades: | 8 bits |

| Resolució ADC: | 12 bits |

| Freqüència màxima de rellotge: | 64 MHz |

| Nombre d'E/S: | 25 E/S |

| Mida de la RAM de dades: | 12,5 kB |

| Tensió d'alimentació - Mín: | 1,8 V |

| Tensió d'alimentació - Màx.: | 5,5 V |

| Temperatura mínima de funcionament: | - 40 °C |

| Temperatura màxima de funcionament: | + 85 °C |

| Embalatge: | Tub |

| Marca: | Tecnologia de microxips / Atmel |

| Sensible a la humitat: | Sí |

| Producte: | MCU |

| Tipus de producte: | Microcontroladors de 8 bits - MCU |

| Quantitat del paquet de fàbrica: | 47 |

| Subcategoria: | Microcontroladors - MCU |

| Nom comercial: | PIC |

♠ Microcontrolador de 28/40/44/48 pins, baix consum i alt rendiment amb tecnologia XLP

La família de microcontroladors PIC18-Q84 està disponible en dispositius de 28/40/44/48 pins per a moltes aplicacions d'automoció i industrials. Els nombrosos perifèrics de comunicació que es troben a la família de productes, com ara la xarxa d'àrea de controlador (CAN), la interfície de perifèrics sèrie (SPI), el circuit interintegrat (I2C), dos transmissors receptors asíncrons universals (UART), poden gestionar una àmplia gamma de protocols de comunicació amb fil i sense fil (mitjançant mòduls externs) per a aplicacions intel·ligents. Combinada amb les capacitats d'integració de perifèrics independents del nucli (CIP), aquesta capacitat permet funcions per a aplicacions de control de motors, font d'alimentació, sensors, senyals i interfície d'usuari. A més, aquesta família inclou un convertidor analògic-digital (ADC) de 12 bits amb extensions de computació i commutació de context per a l'anàlisi automatitzada del senyal per reduir la complexitat de l'aplicació.

• Arquitectura RISC optimitzada per al compilador C

• Velocitat de funcionament:

– Entrada de rellotge CC de 64 MHz

– Cicle d'instrucció mínim de 62,5 ns

• Vuit controladors d'accés directe a memòria (DMA):

– Transferències de dades a espais SFR/GPR des de memòria flash de programa, EEPROM de dades o SFR/GPRespais

– Mides d'origen i destinació programables per l'usuari

– Transferències de dades activades per maquinari i programari

• Capacitat d'interrupció vectoritzada:

– Prioritat alta/baixa seleccionable

– Latència d'interrupció fixa de tres cicles d'instruccions

– Adreça base de taula vectorial programable

– Compatible amb versions anteriors de les capacitats d'interrupció

• Pila de maquinari profunda de 128 nivells

• Restabliment d'encesa per baix corrent (POR)

• Temporitzador d'encesa configurable (PWRT)

• Reinici per caiguda de tensió (BOR)

• Opció BOR de baixa potència (LPBOR)

• Temporitzador de vigilància en finestra (WWDT):

– Reinici del Watchdog en un interval massa llarg o massa curt entre esdeveniments d'esborrat del Watchdog

– Selecció de prescalador variable

– Selecció de mida de finestra variable