TMS320F2812PGFA Processadors i controladors de senyal digital DSP DSC Controlador de senyal digital de 32 bits amb memòria flaix

♠ Descripció del producte

| Atribut del producte | Valor de l'atribut |

| Fabricant: | Texas Instruments |

| Categoria de producte: | Processadors i controladors de senyal digital: DSP, DSC |

| RoHS: | Detalls |

| Producte: | DSCs |

| Sèrie: | TMS320F2812 |

| Nom comercial: | C2000 |

| Estil de muntatge: | SMD/SMT |

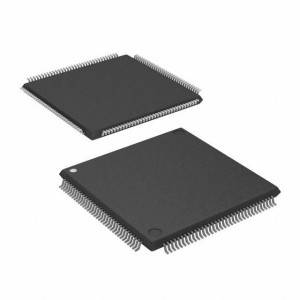

| Paquet / Caixa: | LQFP-176 |

| Nucli: | C28x |

| Nombre de nuclis: | 1 nucli |

| Freqüència màxima de rellotge: | 150 MHz |

| Memòria d'instruccions de la memòria cau L1: | - |

| Memòria de dades de memòria cau L1: | - |

| Mida de memòria del programa: | 256 kB |

| Mida de la RAM de dades: | 36 kB |

| Tensió d'alimentació de funcionament: | 1,9 V |

| Temperatura mínima de funcionament: | - 40 °C |

| Temperatura màxima de funcionament: | + 125 °C |

| Embalatge: | Safata |

| Resolució ADC: | 12 bits |

| Marca: | Texas Instruments |

| Amplada del bus de dades: | 32 bits |

| Voltatge d'E/S: | 3,3 V |

| Tipus d'instrucció: | Punt fix |

| Sensible a la humitat: | Sí |

| Tipus de producte: | DSP - Processadors i controladors de senyal digital |

| Quantitat del paquet de fàbrica: | 40 |

| Subcategoria: | Processadors i controladors integrats |

| Pes unitari: | 0,066886 unces |

• Tecnologia CMOS estàtica d'alt rendiment

– 150 MHz (temps de cicle de 6,67 ns)

– Baixa potència (nucli d'1,8 V a 135 MHz,Nucli d'1,9 V a 150 MHz, disseny de 3,3 VI/O

• Compatibilitat amb l'escaneig de límits JTAG

– Estàndard IEEE 1149.1-1990 Estàndard IEEEProva del port d'accés i Boundary-ScanArquitectura

• CPU d'alt rendiment de 32 bits (TMS320C28x)

– Operacions MAC 16 × 16 i 32 × 32

– MAC dual 16 × 16

– Arquitectura d'autobusos de Harvard

– Operacions atòmiques

– Resposta i processament d'interrupcions ràpids

– Model de programació de memòria unificada

– Abast d'adreça de programa/dades lineal de 4M

– Eficient en codi (en C/C++ i Assembly)

– Codi font del processador TMS320F24x/LF240xcompatible

• Memòria integrada en el xip

– Fins a 128K × 16 flaix(Quatre sectors de 8K × 16 i sis de 16K × 16)

– ROM OTP d'1K × 16

– L0 i L1: 2 blocs de 4K × 16 cadascun de RAM d'accés únic (SARAM)

– H0: 1 bloc de 8K × 16 SARAM

– M0 i M1: 2 blocs de SARAM d'1K × 16 cadascun

• ROM d'arrencada (4K × 16)

– Amb modes d'arrencada per programari

– Taules matemàtiques estàndard

• Interfície externa (F2812)

– Més d'1 M × 16 de memòria total

– Estats d'espera programables

– Temporització estroboscòpica de lectura/escriptura programable

– Tres seleccions individuals de xips

• Endianisme: Little endian

• Control del rellotge i del sistema

– Oscil·lador integrat en un xip

– Mòdul temporitzador de vigilància

• Tres interrupcions externes

• Bloc d'expansió d'interrupcions perifèriques (PIE) queadmet 45 interrupcions perifèriques

• Tres temporitzadors de CPU de 32 bits

• Clau/cadena de seguretat de 128 bits

– Protegeix la memòria flash/OTP i la SARAM L0/L1

– Evita l'enginyeria inversa del firmware

• Perifèrics de control de motors

– Dos gestors d'esdeveniments (EVA, EVB)

– Compatible amb dispositius 240xA

• Perifèrics de port sèrie

– Interfície perifèrica sèrie (SPI)

– Dues interfícies de comunicació en sèrie (SCI),UART estàndard

– Xarxa d'àrea de controlador millorada (eCAN)

– Port sèrie multicanal amb memòria intermèdia (McBSP)

• ADC de 12 bits, 16 canals

– Multiplexor d'entrada de 2 × 8 canals

– Dos mostrejos i retenció

– Conversions simples/simultànies

– Taxa de conversió ràpida: 80 ns/12,5 MSPS

• Fins a 56 pins d'E/S d'ús general (GPIO)

• Funcions d'emulació avançades

– Funcions d'anàlisi i de punt d'interrupció

– Depuració en temps real via maquinari

• Les eines de desenvolupament inclouen

– Compilador/assemblador/enllaçador ANSI C/C++

– IDE de Code Composer Studio™

– DSP/BIOS™

– Controladors d'escaneig JTAG

• Estàndard IEEE 1149.1-1990 Estàndard IEEEProva del port d'accés i Boundary-ScanArquitectura

• Modes de baix consum i estalvi d'energia

– Modes IDLE, STANDBY, HALT compatibles

– Desactiva els rellotges perifèrics individuals

• Opcions de paquet

– MicroStar BGA™ de 179 boles amb memòria externainterfície (GHH, ZHH) (F2812)

– Paquet pla quàdruple de perfil baix de 176 pins (LQFP) ambinterfície de memòria externa (PGF) (F2812)

– LQFP de 128 pins sense memòria externainterfície (PBK) (F2810, F2811)

• Opcions de temperatura

– A: –40 °C a 85 °C (GHH, ZHH, PGF, PBK)

– S: –40 °C a 125 °C (GHH, ZHH, PGF, PBK)

– Q: –40 °C a 125 °C (PGF, PBK)(Qualificació AEC-Q100 per a automoció)

aplicacions)

• Sistemes avançats d'assistència al conductor (ADAS)

• Automatització d'edificis

• Punt de venda electrònic

• Vehicle elèctric/Vehicle híbrid elèctric (EV/HEV)tren motriu

• Automatització de fàbriques

• Infraestructura de xarxa

• Transport industrial

• Medicina, atenció sanitària i fitness

• Accionaments de motor

• Lliurament de potència

• Infraestructura de telecomunicacions

• Prova i mesura