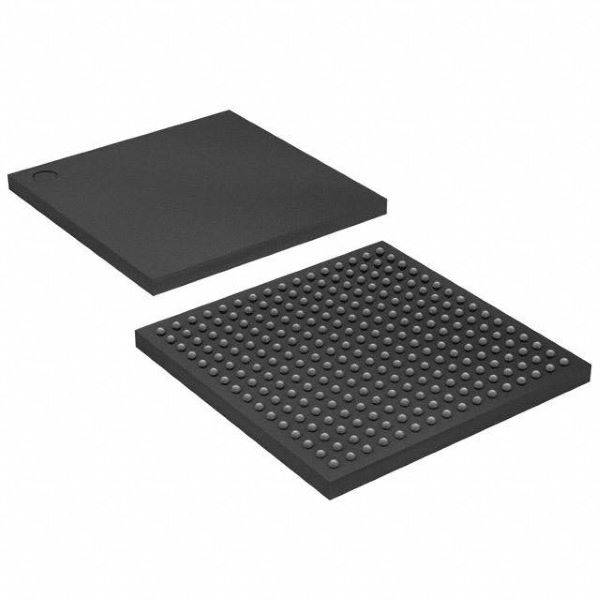

XC6SLX25-2FTG256C FPGA – Matriu de portes programables de camp La fàbrica actualment no accepta comandes per a aquest producte.

♠ Descripció del producte

| Atribut del producte | Valor de l'atribut |

| Fabricant: | Xilinx |

| Categoria de producte: | FPGA - Matriu de portes programables en camp |

| RoHS: | Detalls |

| Sèrie: | XC6SLX25 |

| Nombre d'elements lògics: | 24051 LE |

| Nombre d'E/S: | 186 E/S |

| Tensió d'alimentació - Mín: | 1,14 V |

| Tensió d'alimentació - Màx.: | 1,26 V |

| Temperatura mínima de funcionament: | 0 °C |

| Temperatura màxima de funcionament: | + 85 °C |

| Velocitat de dades: | - |

| Nombre de transceptors: | - |

| Estil de muntatge: | SMD/SMT |

| Paquet/Caixa: | FBGA-256 |

| Marca: | Xilinx |

| RAM distribuïda: | 229 kbit |

| Bloc RAM integrat - EBR: | 936 kbit |

| Freqüència màxima de funcionament: | 1080 MHz |

| Sensible a la humitat: | Sí |

| Nombre de blocs de matriu lògica - LAB: | LABORATORI DE 1879 |

| Tensió d'alimentació de funcionament: | 1,2 V |

| Tipus de producte: | FPGA - Matriu de portes programables en camp |

| Quantitat del paquet de fàbrica: | 1 |

| Subcategoria: | Circuits integrats de lògica programable |

| Nom comercial: | espartà |

| Pes unitari: | 21,576 grams |

♠ Visió general de la família Spartan-6

La família Spartan®-6 ofereix capacitats d'integració de sistemes líders amb el cost total més baix per a aplicacions d'alt volum. La família de tretze membres ofereix densitats ampliades que van des de 3.840 fins a 147.443 cel·les lògiques, amb la meitat del consum d'energia de les famílies Spartan anteriors i una connectivitat més ràpida i completa. Construïda sobre una tecnologia madura de procés de coure de baix consum de 45 nm que ofereix l'equilibri òptim entre cost, potència i rendiment, la família Spartan-6 ofereix una nova lògica de taula de cerca (LUT) de 6 entrades i doble registre més eficient i una àmplia selecció de blocs de nivell de sistema integrats. Aquests inclouen RAM de bloc de 18 Kb (2 x 9 Kb), porcions DSP48A1 de segona generació, controladors de memòria SDRAM, blocs de gestió de rellotge de mode mixt millorats, tecnologia SelectIO™, blocs de transceptor sèrie d'alta velocitat optimitzats per a l'energia, blocs de punt final compatibles amb PCI Express®, modes avançats de gestió d'energia a nivell de sistema, opcions de configuració de detecció automàtica i seguretat IP millorada amb protecció AES i Device DNA. Aquestes característiques proporcionen una alternativa programable de baix cost als productes ASIC personalitzats amb una facilitat d'ús sense precedents. Les FPGA Spartan-6 ofereixen la millor solució per a dissenys lògics d'alt volum, dissenys DSP orientats al consumidor i aplicacions integrades sensibles al cost. Les FPGA Spartan-6 són la base de silici programable per a plataformes de disseny dirigit que ofereixen components de programari i maquinari integrats que permeten als dissenyadors centrar-se en la innovació tan bon punt comença el seu cicle de desenvolupament.

• Família Spartan-6:

• Spartan-6 LX FPGA: Optimitzat lògicament

• Spartan-6 LXT FPGA: Connectivitat sèrie d'alta velocitat

• Dissenyat per a un baix cost

• Múltiples blocs integrats eficients

• Selecció optimitzada d'estàndards d'E/S

• Coixinets esglaonats

• Envasos de plàstic de gran volum enllaçats amb filferro

• Baixa potència estàtica i dinàmica

• Procés de 45 nm optimitzat per cost i baix consum

• Mode d'hibernació i apagada per a zero energia

• El mode de suspensió manté l'estat i la configuració amb activació multipin i millora del control

• Voltatge del nucli de menor potència d'1.0V (FPGA LX, només -1L)

• Voltatge de nucli d'alt rendiment d'1,2 V (FPGA LX i LXT, graus de velocitat de -2, -3 i -3N)

• Bancs d'interfície SelectIO™ multitensió i multiestàndard

• Velocitat de transferència de dades de fins a 1.080 Mb/s per E/S diferencial

• Sortida seleccionable, fins a 24 mA per pin

• Estàndards i protocols de 3,3 V a 1,2 VI/O

• Interfícies de memòria HSTL i SSTL de baix cost

• Compliment de canvi en calent

• Velocitats de variació d'E/S ajustables per millorar la integritat del senyal

• Transceptors sèrie GTP d'alta velocitat a les FPGA LXT

• Fins a 3,2 Gb/s

• Interfícies d'alta velocitat que inclouen: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort i XAUI

• Bloc de punt final integrat per a dissenys PCI Express (LXT)

• Compatibilitat amb la tecnologia PCI® de baix cost, compatible amb les especificacions de 33 MHz, 32 i 64 bits.

• Seccions DSP48A1 eficients

• Aritmètica i processament de senyals d'alt rendiment

• Multiplicador ràpid de 18 x 18 i acumulador de 48 bits

• Capacitat de canalització i cascada

• Preafegidor per ajudar a l'aplicació del filtre

• Blocs de controlador de memòria integrats

• Compatibilitat amb DDR, DDR2, DDR3 i LPDDR

• Velocitats de dades de fins a 800 Mb/s (amplada de banda màxima de 12,8 Gb/s)

• Estructura de bus multiport amb FIFO independent per reduir els problemes de temps de disseny

• Recursos lògics abundants amb una major capacitat lògica

• Compatibilitat opcional amb registre de desplaçament o RAM distribuïda

• Les LUT eficients de 6 entrades milloren el rendiment i minimitzen el consum d'energia

• LUT amb dobles flip-flops per a aplicacions centrades en la canonada

• Bloc de RAM amb una àmplia gamma de granularitat

• RAM de bloc ràpida amb habilitació d'escriptura de bytes

• Blocs de 18 Kb que es poden programar opcionalment com a dues RAM de blocs independents de 9 Kb

• Tessel·la de gestió del rellotge (CMT) per a un rendiment millorat

• Rellotge flexible i baix soroll

• Els gestors de rellotge digital (DCM) eliminen el biaix del rellotge i la distorsió del cicle de treball

• Bucles de bloqueig de fase (PLL) per a un rellotge de baixa fluctuació

• Síntesi de freqüència amb multiplicació, divisió i canvi de fase simultanis

• Setze xarxes de rellotge globals de baixa asimetria

• Configuració simplificada, compatible amb estàndards de baix cost

• Configuració de detecció automàtica de 2 pins

• Ampli suport per a SPI de tercers (fins a x4) i memòria flaix NOR

• Plataforma flash Xilinx rica en funcions amb JTAG

• Compatibilitat amb MultiBoot per a l'actualització remota amb múltiples fluxos de bits, mitjançant la protecció de watchdog

• Seguretat millorada per a la protecció del disseny

• Identificador únic d'ADN del dispositiu per a l'autenticació del disseny

• Xifratge de flux de bits AES en els dispositius més grans

• Processament integrat més ràpid amb un processador MicroBlaze™ suau millorat i de baix cost

• Dissenys de referència i IP líders en la indústria