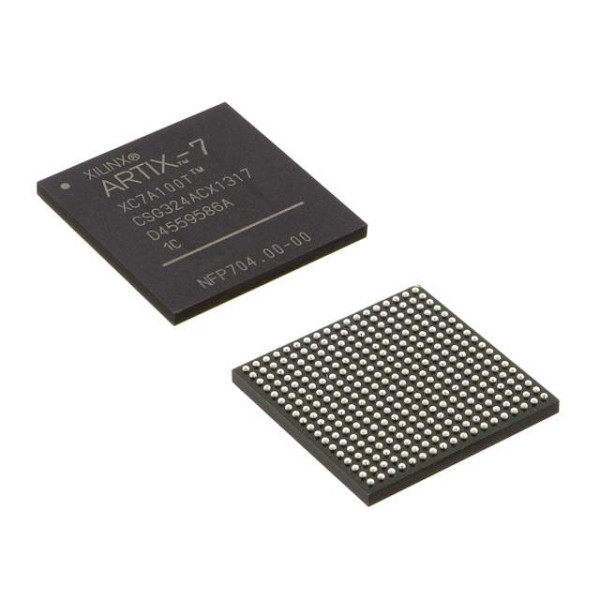

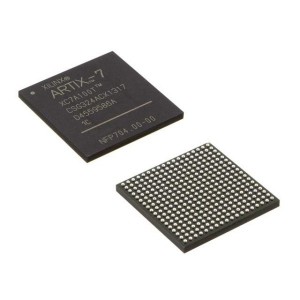

XC7A50T-2CSG324I FPGA – Matriu de portes programables de camp XC7A50T-2CSG324I

♠ Descripció del producte

| Atribut del producte | Valor de l'atribut |

| Fabricant: | Xilinx |

| Categoria de producte: | FPGA - Matriu de portes programables en camp |

| Sèrie: | XC7A50T |

| Nombre d'elements lògics: | 52160 LE |

| Nombre d'E/S: | 210 E/S |

| Tensió d'alimentació - Mín: | 0,95 V |

| Tensió d'alimentació - Màx.: | 1,05 V |

| Temperatura mínima de funcionament: | - 40 °C |

| Temperatura màxima de funcionament: | + 100 °C |

| Velocitat de dades: | - |

| Nombre de transceptors: | - |

| Estil de muntatge: | SMD/SMT |

| Paquet / Caixa: | CSBGA-324 |

| Marca: | Xilinx |

| RAM distribuïda: | 600 kbit |

| Bloc RAM integrat - EBR: | 2700 kbit |

| Sensible a la humitat: | Sí |

| Nombre de blocs de matriu lògica - LAB: | 4075 LAB |

| Tensió d'alimentació de funcionament: | 1 V |

| Tipus de producte: | FPGA - Matriu de portes programables en camp |

| Quantitat del paquet de fàbrica: | 1 |

| Subcategoria: | Circuits integrats de lògica programable |

| Nom comercial: | Artix |

| Pes unitari: | 1 unça |

♠ Les FPGA de la sèrie 7 de Xilinx® comprenen quatre famílies de FPGA que satisfan tota la gamma de requisits del sistema, des d'aplicacions de baix cost, format reduït i sensibles al cost i gran volum fins a amplada de banda de connectivitat d'ultra alta gamma, capacitat lògica i capacitat de processament de senyals per a les aplicacions d'alt rendiment més exigents.

Les FPGA de la sèrie 7 de Xilinx® comprenen quatre famílies de FPGA que cobreixen tota la gamma de requisits del sistema, des d'aplicacions de baix cost, format reduït i d'alt volum, sensibles al cost, fins a un ample de banda de connectivitat d'ultra alta gamma, capacitat lògica i capacitat de processament de senyals per a les aplicacions d'alt rendiment més exigents. Les FPGA de la sèrie 7 inclouen:

• Família Spartan®-7: Optimitzada per a un baix cost, un consum d'energia més baix i un alt rendiment d'E/S. Disponible en un embalatge de baix cost i format molt petit per a una petjada de PCB mínima.

• Família Artix®-7: Optimitzada per a aplicacions de baix consum que requereixen transceptors sèrie i un alt rendiment DSP i lògic. Proporciona el cost total de la factura de materials més baix per a aplicacions d'alt rendiment i sensibles al cost.

• Família Kintex®-7: Optimitzada per a la millor relació qualitat-preu amb una millora del doble en comparació amb la generació anterior, cosa que permet una nova classe de FPGA.

• Família Virtex®-7: Optimitzat per al màxim rendiment i capacitat del sistema amb una millora del doble en el rendiment del sistema. Dispositius de màxima capacitat habilitats per la tecnologia d'interconnexió de silici apilat (SSI).

Construïdes sobre una tecnologia de procés d'última generació, d'alt rendiment, baix consum (HPL), 28 nm i porta metàl·lica d'alta k (HKMG), les FPGA de la sèrie 7 permeten un augment sense precedents del rendiment del sistema amb 2,9 Tb/s d'ample de banda d'E/S, una capacitat de 2 milions de cel·les lògiques i un DSP de 5,3 TMAC/s, alhora que consumeixen un 50% menys d'energia que els dispositius de la generació anterior per oferir una alternativa totalment programable als ASSP i ASIC.

• Lògica FPGA avançada d'alt rendiment basada en tecnologia de taula de cerca (LUT) real de 6 entrades configurable com a memòria distribuïda.

• RAM de bloc de doble port de 36 Kb amb lògica FIFO integrada per a l'emmagatzematge intermedi de dades en el xip.

• Tecnologia SelectIO™ d'alt rendiment amb compatibilitat amb interfícies DDR3 de fins a 1.866 Mb/s.

• Connectivitat sèrie d'alta velocitat amb transceptors multigigabit integrats des de 600 Mb/s fins a velocitats màximes de 6,6 Gb/s fins a 28,05 Gb/s, que ofereix un mode especial de baix consum, optimitzat per a interfícies xip a xip.

• Una interfície analògica configurable per l'usuari (XADC), que incorpora convertidors analògic-digital duals de 12 bits i 1 MSPS amb sensors tèrmics i de subministrament integrats.

• Segells DSP amb multiplicador de 25 x 18, acumulador de 48 bits i preadditor per a un filtratge d'alt rendiment, inclòs un filtratge de coeficients simètrics optimitzat.

• Potents tessel·les de gestió de rellotge (CMT), que combinen blocs de bucle de bloqueig de fase (PLL) i gestors de rellotge de mode mixt (MMCM) per a una alta precisió i baixa fluctuació.

• Implementeu ràpidament el processament integrat amb el processador MicroBlaze™.

• Bloc integrat per a PCI Express® (PCIe), per a dissenys de ports arrel i de punt final de 3a generació (endpoint) de fins a x8.

• Àmplia varietat d'opcions de configuració, incloent-hi compatibilitat amb memòries estàndard, xifratge AES de 256 bits amb autenticació HMAC/SHA-256 i detecció i correcció SEU integrades.

• Encapsulat de baix cost, amb cablejat, circuits integrats i encapsulat de xip flexible d'alta integritat de senyal que ofereix una migració fàcil entre membres de la família en el mateix encapsulat. Tots els encapsulats estan disponibles sense plom i encapsulats seleccionats amb l'opció de plom.

• Dissenyat per a un alt rendiment i una potència mínima amb 28 nm, procés HKMG, HPL, tecnologia de procés de voltatge de nucli d'1.0V i opció de voltatge de nucli de 0.9V per a una potència encara menor.